|

|

Процессор как совокупность автоматов

Для более ясного понимания принципов работы процессора будем рассматривать процессор как набор автоматов, и заново рассмотрим принцип микропрогаммного управления процессором.

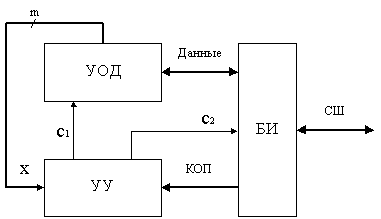

Любой процессор обычно содержит три основные части: устройство обработки данных , состоящее из набора операционных устройств иначе АЛУ, устройство управления (УУ) и блок интерфейса (БИ) для сопряжения с системной магистралью (рис. 1).

Рис. 1. Структура процессора

Устройство обработки данных процессора АЛУ-представляет собой операционный автомат, реализующий алгоритмы выполнения арифметических и логических операций.

Устройство управления процессора представляет собой управляющий автомат, предназначенный для выработки в каждом такте работы процессора векторов управляющих сигналов: с1 – для управления АЛУ и с2 – для управления устройствами БИ. Входной информацией для выработки управляющих сигналов является код операции (КОП), выполняемой процессором, и вектор осведомительных сигналов  , информирующий УУ о состоянии АЛУ и результатах выполнения предыдущих микроопераций.

, информирующий УУ о состоянии АЛУ и результатах выполнения предыдущих микроопераций.

Блок интерфейса процессора представляет собой автомат, выполняющий функции операционного и управляющего автоматов. Он обеспечивает взаимодействие процессора со всеми внешними устройствами. В их число входят: узел управления шинами – управляющий автомат; узел формирования адресов памяти– операционный автомат; буферные схемы и некоторые другие вспомогательные узлы – выполняющие функции электрического согласования.

Операционный автомат – устройство, объединяющее все функциональные модули, непосредственно занятые обработкой информации, ее хранением, пересылкой и т.п. У этих модулей имеются информационные входы и выходы, управляющие входы z1, z2, ..., а также выходы u1, u2,..., которые сигнализируют о состоянии вычислительного процесса (код знака операнда, признак переноса, признак обнуления результата и др.). Эти выходы мы будем называть осведомительными сигналами, или внутренними логическими условиями устройства.

Осведомительные сигналы - выходные сигналы операционного автомата, информирующие о состоянии вычислительного процесса (код знака операнда, признак переноса, признак обнуления результата и др.)

Управляющий автомат это устройство, вырабатывающее сигналы управления z по заданной программе и с учетом значений внутренних и внешних логических условий u, которые для него являются входными переменными. Внешние логические условия задают одну из нескольких возможных в данном устройстве микропрограмм.

Управляющие автоматыУправляющий автомат (УА) можно строить двумя способами.

Управляющий автомат с жесткой логикой – специальная логическая сеть с элементами памяти, реализующая микропрограмму выполнения команды. Структура сети определяется теми микропрограммами, которые должны выполняться данным устройством. При этом способе можно свести к минимуму объем оборудования и, что бывает гораздо важнее, обеспечить максимально возможное быстродействие. Зато проектирование такого управления является делом долгим и сложным, а перепрограммирование УА на другую работу вообще невозможно.

Микропрограммный УА, или управляющий автомат с программируемой логикой,строится с использованием специальной встроенной памяти микропрограмм. В эту память записываются все требуемые микропрограммы, а от схемы управления требуется только организация чтения микропрограмм. Проектирование микропрограммного автомата несравненно проще, так как в нем используются типовые аппаратные модули. Единственной специальной задачей, решаемой в рамках теории автоматов, остается абстрактный синтез и составление таблиц программирования памяти. Недостатками микропрограммного управления является некоторая избыточность оборудования и меньшее быстродействие.

Определим некоторые общие понятия и функциональное назначение устройства управления. Определим, прежде всего, понятие микрокоманды, а также взаимосвязанных с ним понятий микрооперации и микропрограммы.

Программа представляет собой совокупность команд, записанных в определенной последовательности, которая обеспечивает решение данной конкретной задачи на компьютере.

Команда - это инструкция для выполнения очередного этапа в вычислениях, а также соответствующее обозначение этой инструкции.

Операция - действие, выполняемое в компьютере или процессоре под воздействием команды. При этом каждой команде соответствует операция, выполняемая процессором.

Практически в любом процессоре операция не является элементарным действием. Она состоит из последовательности нескольких других элементарных действий, которые называют микрооперациями. При этом одна или несколько совместимых во времени микроопераций выполняются за один элементарный интервал времени, представляющий собой период синхронизирующих (тактовых) импульсов и называемый тактом.

Таким образом, операция, выполняемая в процессоре под воздействием какой-либо команды, представляет собой ряд микроопераций. Каждая из микроопераций или несколько из них, выполняемых в один такт, реализуется в устройствах компьютера или процессора под воздействием микрокоманды. Следовательно, каждой команде соответствует своя совокупность микрокоманд. Эту совокупность микрокоманд, или микроинструкций, реализующих данную команду, называют микропрограммой.

Из изложенного видно, что в каждом такте в любом процессоре должна быть сформирована своя микрокоманда, или микроинструкция, которая и обеспечивает выполнение необходимых микроопераций. На рис. 4 представлена диаграмма, на которой по горизонтальной оси отображена последовательность тактов, а по вертикальной - номера цепей управления процессора при выполнении им некой команды. Каждому такту и каждой цепи управления поставлен в соответствие определенный уровень управляющего сигнала. Например, единичный уровень сигнала является разрешающим, а нулевой - запрещающим. Следует заметить, что для некоторых цепей за разрешающий может быть принят и нулевой уровень.

Рис. 4. Диаграмма распределения управляющих сигналов процессора по цепям управления и по тактам: u1,u2,u3 – коды команд

Из диаграммы видно, что в каждом такте на управляющие цепи процессора (общее число их может составлять 40 - 60 и более) должна быть подана своя совокупность сигналов управления, разрешающих или запрещающих какую-то микрооперацию. Эту совокупность сигналов управления и называют микрокомандой, или управляющим словом. Считают, что в тех тактах, в которых имеются несколько разрешающих сигналов, одновременно выполняется несколько элементарных действий – микроопераций. Но при этом в каждом такте имеется только одно управляющее слово, т.е. реализуется одна микрокоманда.

Таким образом, при выполнении любой команды в процессоре должна быть сформирована совокупность управляющих сигналов, распределенных в пространстве (по цепям управления) и во времени (по тактам). Эта совокупность управляющих сигналов и представляет собой микропрограмму, реализующую данную команду.

Формирование управляющих сигналов для всех цепей управления в каждом такте осуществляется устройством управления процессора. Как видим, задача формирования управляющих сигналов является достаточно сложной и громоздкой, если принять во внимание при этом, что в процессоре имеется достаточно большое число цепей управления и значительное число команд (до 130 и более), причем каждая команда выполняется за несколько тактов (до 5 – 10 и более). Кроме того, устройство управления должно реагировать также на внешние сигналы управления.

В настоящее время для построения устройства управления в процессорах используются два принципа: 1) на основе аппаратной реализации или «жесткой» логики управления и 2) на основе микропрограммной реализации или «гибкой» логики управления. Рассмотрим кратко оба этих принципа. Но вначале необходимо рассмотреть некоторые общие узлы, которые используются при реализации обоих принципов построения устройства управления.

Регистр команды предназначен для приема и хранения кода операции команды, считанной из ОЗУ, на время ее выполнения процессором. Разрядность регистра команды равна разрядности шины данных процессора. В связи с этим в 8-разрядных процессорах в регистр команд заносится и хранится там первый байт команд, а в 16-разрядных - первое слово команды. И в том, и в другом случае содержимое регистра команды несет в себе информацию о коде операции и об используемом в данной операции способе адресации. При этом другие байты, или слова команды, которые несут в себе адресную информацию или являются непосредственными данными, принимаются другими регистрами процессора.

Дешифратор командыявляется обязательным узлом любого устройства управления процессора. Это функциональное комбинационное устройство, предназначенное для расшифровывания кода операции команды для использования в других узлах устройства управления.

В устройствах управления и на основе «жесткой» логики, и на основе «гибкой» логики часто используются так называемые программируемые логические матрицы (ПЛМ). Это логическая сеть, состоящая из двух ступеней: матрицы логических элементов «И», связанной с матрицей логических элементов «ИЛИ», связи между элементами задаются однократно путем «прожига» отдельных «ненужных» перемычек.

Во многих современных процессорах есть узел, который называют очередью команд. Очередь команд представляет собой запоминающее устройство, предназначенное для хранения очередных, подлежащих выполнению команд.

Заполнение буферной памяти команд производится в интервалы времени, когда шина данных процессора не занята им для обмена данными с основной памятью или внешними устройствами. Выборка команд из очереди команд производится процессором по мере их выполнения. Таким образом обеспечивается повышение общей производительности процессора, поскольку практически не требуется дополнительных затрат времени на выборку команд из оперативного запоминающего устройства - очередные команды уже находятся во внутренней буферной памяти процессора. Полное время на выборку команды с обращением к оперативному запоминающему устройству тратится лишь в тех случаях, когда производится передача управления при реализации условных переходов в программе. В этих случаях производится реинициализация очереди команд и загрузка ее новой последовательностью команд. При этом первая же выбранная из ОЗУ команда становится сразу доступной для выполнения. Одной из разновидностей реализации очереди команд является так называемая КЭШ-память, размещаемая непосредственно на кристалле процессора. В ряде современных процессоров КЭШ-память используется при этом как буферное запоминающее устройство не только для потока команд, но также и для потока данных. Емкость такого буферного запоминающего устройства достигает 256 байт и более.