|

|

Задающие генераторы

Основным требованием, предъявляемым к задающим генераторам (ЗГ) ЦСП, является стабильность частоты. В то же время они должны иметь возможность перестройки частоты в определенных пределах. Выполнение противоречивых требований обеспечения стабильности частоты ЗГ (в режиме автогенерации) и реализации определенной перестройки учитывается при выборе соответствующей схемы ЗГ. Относительная нестабильность частоты ЗГ должна быть не выше 10~5, и поэтому в схемах ЗГ для стабилизации частоты используются кварцевые резонаторы (КР). Частота

Рис. 2.17. Принципиальная схема ЗГ на транзисторах

ЗГ выбирается в целое число большей, чем тактовая частота ƒт. Так, например, ЗГ аппаратуры формирования первичного цифрового потока типа ИКМ-30 вырабатывает гармоническое колебание с частотой ƒзг = 8192 кГц. Выбор частоты генерации, в 4 раза превышающей тактовую частоту потока, позволяет осуществить почти оптимальное построение ЗГ. В схему ЗГ входят делитель частоты (ДЧ) и формирователь тактовой последовательности (ФТП). В настоящее время ЗГ цифровых систем передачи реализуются как на дискретных (рис. 2.17), так и на логических элементах (рис. 2.18).

Рис. 2.18. Функциональная схема ЗГ на логических элементах

Схема ЗГ (рис. 2.17) представляет двухкаскадный усилитель с положительной обратной связью, в состав которого входит кварцевый резонатор КР. Режим по постоянному току первого каскада обеспечивается резисторами R1...R4, второго - резисторами R5...R6. Для изменения частоты ЗГ в заданных пределах включен варикап VD, управляемый напряжением Uуп, которое может изменяться или регулироваться устройством фазовой автоподстройки частоты при работе ЗГв режиме внешней синхронизации.

Схема ЗГ (рис. 2.18) состоит из трех инверторов DDI...DD3, сопротивлений R1 и R5 обеспечивают перевод элементов DI и D2 в активный режим. Длительность импульсов можно менять подборкой резисторов R1 и R6, сопротивления которых совместно с входной емкостью элемента DD3 образуют цепь временной задержки. Подстройка частоты осуществляется управляемым варикапом VD.

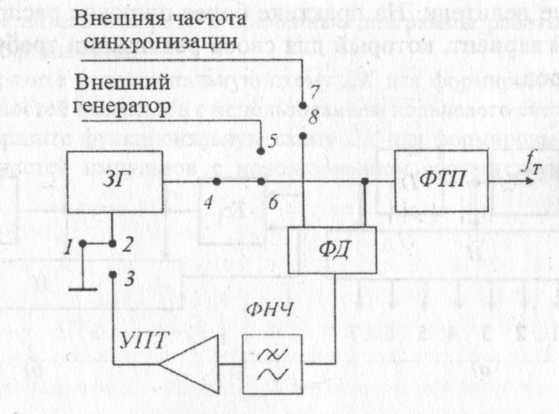

Учитывая, что ЗГ должен работать в режиме как автогенерации, так и внешнего управления частотой в схеме предусматривается возможность переключения режимов. На рис. 2.19 представлена схема задающего генератора, включающая в себя автогенератор с кварцевой стабилизацией, собственно ЗГ и схему фазовой автоподстройки частоты (ФАПЧ), состоящей из фазового детектора - ФД, фильтра нижних частот - ФНЧ и усилителя постоянного тока, формирующих сигнал управления перестройкой частоты ЗГ.

Рис. 2.19. Схема ЗГ с фазовой автоподстройкой частоты

В режиме автогенерации устанавливаются перемычки 1 - 2, 4 - 6, а в режиме внешней подстройки частоты - перемычки 2-3, 4 - 6 и 7 - 8. При этом в работу включается схема ФАПЧ, которая сравнивает фазы внешней частоты синхронизации и собственной частоты ЗГ. Если имеются расхождения фаз этих частот, то вырабатывается соответствующий управляющий сигнал, и частота ЗГ подстраивается под частоту синхронизации.

В режиме использования внешнего генератора устанавливается перемычка 5-6. Работа схемы от местного генератора и работа от внешнего генератора совершенно одинаковы.

В режиме внешней синхронизации схема работает следующим образом: устанавливается перемычка 7-8; частота местного ЗГ и частота от внешнего генератора поступают на фазовый детектор ФД на выходе которого образуется разностный сигнал; ФНЧ выделяет постоянную составляющую этого сигнала, величина которой пропорциональна расхождению частот воздействующих на него сигналов; сигнал с выхода ФНЧ усиливается У/7Г, на выходе которого формируется сигнал напряжением Uуп, управляющий перестройкой частоты ЗГ (воздействуя, к примеру, на варикап).

Делители частоты

Схемы делителей различного назначения (разрядных, канальных, циклов и сверхциклов) легко реализуются на основе счетчиков, регистров, дешифраторов и других логических схем.

Функциональная схема делителя разрядов ДР (для m = 8) с использованием трехразрядного двоичного счетчика на триггерах Тг1... Tг3 показана на рис. 2.20,а.

Реализовать такой ДР можно и применением кольцевого счетчика из восьми триггеров Тг1...Тг8, рис. 2.20,б. Аналогичным образом можно построить и другие делители. На практике более широкое распространение получил первый вариант, который для своей реализации требует меньшего числа триггеров.

Рис. 2.20. Функциональные схемы делителей разрядов