|

|

Источники прерываний, их приоритеты и коды векторов

Подсистема контроллера прерываний (8259А)

Все запросы на аппаратные прерывания из системной шины направляются через контроллеры прерываний 8259A. Эти контроллеры генерируют запросы прерываний на вход INTR микропроцессора, которые могут маскироваться в процессоре.

Контроллеры прерываний могут принимать сигналы прерываний от нескольких устройств, назначать им приоритеты и прерывать работу процессора.

|

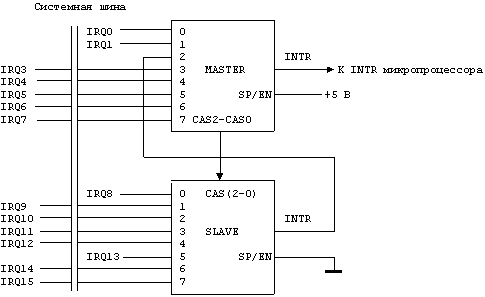

В архитектуре PC AT подсистема аппаратных прерываний состоит из двух контроллеров 8259А (главного - MASTER и подчиненного - SLAVE). Они объединены таким образом, что могут обслужить 15 запросов на прерывания. На рис. 6.13 показана подсистема контроллеров 8259А в PC AT. (Схема электрическая принципиальная подсистемы контроллеров прерывания конкретной РС АТ приведена на Схеме 15, Приложение А). Выход INTR SLAVE соединяется с входом запроса на прерывание (IRQ) MASTER (для PC AT это IRQ2). Таким образом, SLAVE будет прерывать MASTER. Выход INTR MASTER соединен с входом INTR микропоцессора, что обеспечивает общий запрос на прерывания INTR. Выводы каскадирования (CAS2-CAS0) контроллеров объединены и образуют локальную шину между контроллерами, по которой MASTER сообщает SLAVE, что он должен управлять шиной данных (XD7-XD0) в цикле подтверждения прерываний.

Рис. 6.13. Структурная схема подсистем контроллеров 8259А в PC АТ

Порты контроллеров 8259А.

Контроллеры для работы в системе должны быть запрограммированы. Это можно сделать с помощью команд контроллера, которые активизируются командами ввода-вывода микропроцессора. Команды 8259А делятся на команды инициализации (ICW) и рабочие команды (OCW).

Необходимые условия для программирования основных режимов работы 8259A приведены в табл. 6.6.

Табл. 6.6. Условия для программирования основных режимов работы контроллера 8259A.

| Адрес порта | Команда микропроцессора | Константа в AL | Тип командного слова | Команда контроллера |

| 20h, A0h | OUT | OCW2 | Выполнить обычное EOI | |

| 6Х | OCW2 | Выполнить специальное EOI | ||

| А0 | OCW2 | Выполнить ротацию при обычном EOI | ||

| EX | OCW2 | Выполнить ротацию при специальном EOI | ||

| OCW2 | Установить триггер ротациидля AEOI | |||

| OCW2 | Сбросить триггер ротации для AEOI | |||

| 0B | OCW3 | Установить режим чтения регистра ISR | ||

| 0А | OCW3 | Установить режим чтения регистра IRR | ||

| OCW3 | Установить режим специального маскирования SMM | |||

| OCW3 | Сбросить режим специального маскирования SMM | |||

| 0С | OCW3 | Выполнить режим опроса | ||

| ICW1 | Установить каскадный режим, режим распознавания IRQ по фронту и условие выполнения для ICW4 | |||

| 21h, Alh | OUT | XX | OCW1 | Установить регистр IMR |

| XX | ICW2 | Установить код вектора прерываний | ||

| ICW3 | Установить код 04 для MASTER, это значит, что к IRQ2 подключен SLAVE | |||

| ICW3 | Установить адрес SLAVE. Адрес соответствует номеру IRQ master, к которому подключен SLAVE | |||

| ICW4 | Работа в системах m86 | |||

| ICW4 | Установить режим AEOI | |||

| ICW4 | Установить режим SFNM | |||

| ICW4 | Установить режим AEOI и SFNM | |||

| 20h, A0h | IN | - | Чтение текущего ISR или IRR в зависимости от последней команды OCW3 | |

| 21h, A1h | IN | - | Чтение текущего IMR |

Примечание: 20h, 21h - MASTER; A0h, A1h - SLAVE; X - значение, задаваемое пользователем.

Источники прерываний, их приоритеты и коды векторов

После включения питания MASTER и SLAVE инициализируются BIOS, в результате чего каждому запросу на прерывание устанавливается приоритет и присваивается код вектора. В табл. 6.7 указаны источники прерываний, их приоритеты и коды векторов, выдаваемых на шину данных.

Табл. 6.7. Источники прерываний, их приоритеты и коды векторов.

| MASTER/ SLAVE | Запрос на прерывание | Источник прерывания | Приоритет | Код вектора |

| - | NMI** | Ошибка паритета памяти или другая неисправимая ошибка в системе | 02h | |

| MASTER | IRQ0 | Системный таймер | 08h | |

| MASTER | IRQ1 | Клавиатура | 09h | |

| SLAVE | IRQ8 | Часы реального времени | 70h | |

| SLAVE | IRQ9 | Резерв (устройство PnP) | 71h* | |

| SLAVE | IRQ10 | Резерв (Видеоконтроллер) | 72h | |

| SLAVE | IRQ11 | Резерв (Мышь PS/2) | 73h | |

| SLAVE | IRQ12 | Резерв (устройство PnP) | 74h | |

| SLAVE | IRQ13 | Ошибка сопроцессора | 75h | |

| SLAVE | IRQ14 | НМД (Жесткий диск №1) | 76h | |

| SLAVE | IRQ15 | Резерв (Жесткий диск №2) | 77h | |

| MASTER | IRQ3 | Порт COM2 (RS 232C-2) | 0Bh | |

| MASTER | IRQ4 | Порт COM2 (RS 232C-1) | 0Ch | |

| MASTER | IRQ5 | Параллельный порт 2 (LPT2) | 0Dh | |

| MASTER | IRQ6 | НГМД | 0Eh | |

| MASTER | IRQ7 | Параллельный порт 1 (LPT1) | 0Fh |

* Программно переназначается на вектор 0Ah командой INT 0Ah.

** Запрос прерывания NMI маскируется разрядом 7 порта 070h.