|

|

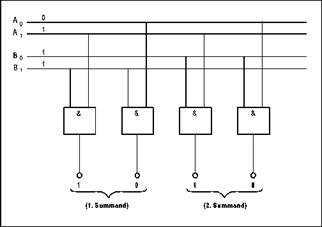

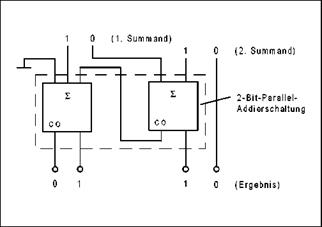

Разрядная параллельная схема умножения

❒ Эксперимент 1:

A 1 A 0 x B 1 B 2

1 0 1 1

1 0 1-ое слагаемое

1 0 1-ое слагаемое

1 0 2-ое слагаемое

1 1 0

1 1 0

|

|

|

Рисунок 6.2.7.1

Рисунок 6.2.7.2

|

| ||||||||||

|

| ||||||||||

|

|

|

| ||||||||

Рисунок 6.2.7.3 3 2-разрядная параллельная схема умножения

Вычислительное устройство для 4-разрядных двоичных чисел

❒ Эксперимент 1:

| Уровень режима работы | Число P | Число Q | CO | Σ 3 | Σ 2 | Σ 1 | Σ 0 | CI | Vorz. | Перенос | Выполненная вычислительная операция | ||||||

| P3 | P2 | P1 | P0 | Q3 | Q2 | Q1 | Q0 | ||||||||||

| L | P + Q | ||||||||||||||||

| L | P + Q | ||||||||||||||||

| L | P + Q | ||||||||||||||||

| L | P + Q | ||||||||||||||||

| L | P + Q | ||||||||||||||||

| H | P - Q, P > Q | ||||||||||||||||

| H | P - Q, P > Q | ||||||||||||||||

| H | P - Q, P < Q | ||||||||||||||||

| H | P - Q, P < Q | ||||||||||||||||

| H | P - Q, P = Q | ||||||||||||||||

| H | P - Q, P = Q |

Таблица 6.2.8.1

Таблица 6.2.8.1

Вопрос 1:Какая вычислительная операция выбирается высоким уровнем напряжения (режим работы)?

Вопрос 3:Какая разница получается при сложении или вычитании чисел P = 0 и Q = 0? Обоснуйте свое мнение.

|  |

Ответ:Вычитание.

Вопрос 2:Как можно определить отрицательный результат?

Вопрос 2:Как можно определить отрицательный результат?

Ответ:Выход знака (плюса или минуса) приводит в действие высокий уровень напряжения.

Ответ:Выход знака (плюса или минуса) приводит в действие высокий уровень напряжения.

Ответ:При P - Q результат будет -0 (минус ноль), при P + Q наоборот +0 (плюс ноль). Выход CO от D6 при проведении обеих вычислительных операции приводит в действие низкий уровень напряжения. Тем самым в случаях вычитания на обоих входах D7 прилегает высокий уровень напряжения, а также на выходе D7.

Счетные схемы