|

|

Преобразователь кода, кодирующее устройство

Двоично-десятичный код 8421 / преобразователь кода с избытком три кода

❒ Эксперимент 1:

| Десятич. значение | Входы: двоично-десятичные коды | Выходы: десятичные коды | ||||||||||||

| 23 | 22 | 21 | 20 | |||||||||||

| d | c | b | a | e | f | g | h | i | j | k | l | m | n | |

|

Таблица 5.2.1.1

Учитывая псевдотетрады, можно провести следующие упрощения:

Рисунок 5.2.1.2 Условное обозначение

|

Рисунок 5.2.1.1 Схема двоично-десятичного кода 8421 / десятичного преобразователя кода

Двоично-десятичный код 8421 / 7-сегментный преобразователь кода

❒ Эксперимент 1

| Входы: двоично-десятичные коды | Цифры | Выходы: 7-сегментные показатели | |||||||||

| a | b | c | d | e | f | g | |||||

| D | C | B | A | ||||||||

Таблица 5.2.2.1

|

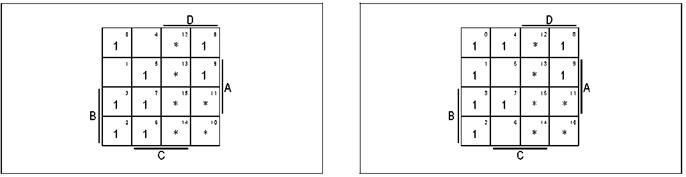

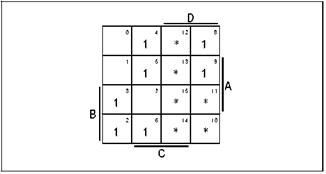

Рисунок 5.2.2.3 3 KV-диаграмма для a

Рисунок 5.2.2.4 KV-диаграмма для b

|

Рисунок 5.2.2.5 KV-диаграмма для c

Рисунок 5.2.2.6 KV-диаграмма для d

|

Рисунок 5.2.2.7 KV-диаграмма для е

Рисунок 5.2.2.8 KV-диаграмма для f

|

Рисунок 5.2.2.9 KV-диаграмма для g

Минимизированные уравнения:

|

Примечания:

Рисунок 5.2.2.10 Схема 2 двоично-десятичного кода 8421 / 7-сегментного преобразователя кода

Схемы кодирующего устройства

❒ Эксперимент 1:

| Двоично-десятичный код 8421 | Схема 1 | Схема 2 | |||||||||

| d | c | b | a | h | g | f | e | h | g | f | e |

Таблица 5.2.3.1

|

Рисунок 5.2.3.3 Условное обозначение для схемы 1 Рисунок 5.2.3.4 Условное обозначение для схемы 2

Примечания:

|

Вычислительные схемы

Полусумматор

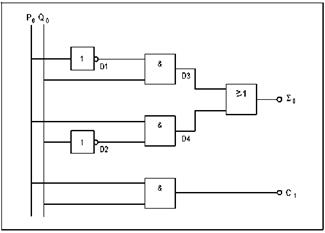

❒ Эксперимент 1: Полусумматор, состоящий из основных элементов

| Слагаемые | Выходы логических элементов | Сумма | |||||

| P0 | Q0 | D1 | D2 | D3 | D4 | Σ 0 | C1 |

Таблица 6.2.1.1

Рисунок 6.2.1.2 Схема

Рисунок 6.2.1.1

❒ Эксперимент 2: Полусумматор, состоящий только из элементов НЕ-И

| Слагаемые | Выходы логических элементов | Сумма | ||||||

| P0 | Q0 | D1 | D2 | D3 | D4 | D5 | Σ 0 | C1 |

Рисунок 6.2.1.3 Схема

Полный сумматор

❒ Эксперимент 1: Одноразрядный полный сумматор

| P1 | Q1 | CI | Σ | CO |

Таблица 6.2.1.2

Таблица 6.2.2.1

Рисунок 6.2.2.1 1 KV-диаграмма для суммы Σ Рисунок 6.2.2.2 2 KV-диаграмма для суммы CO

Рисунок 6.2.2.3 Схема одноразрядного полного сумматора

Примечания:

❒ Эксперимент 2: 2-битный полный сумматор

| P1 | Q1 | P0 | Q0 | CO | Σ 1 | Σ 0 |

|

| Рисунок 6.2.2.4 Схема 2-битного полного сумматора |

Таблица 6.2.2.2