|

|

МИКРОСХЕМНАЯ РЕАЛИЗАЦИЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

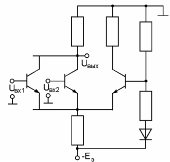

| Тип логики | Схема | Логический элемент | |

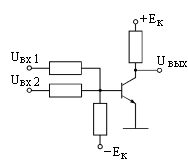

| РТЛ резисторно-транзисторная логика | Микросхема на базе простых транзисторных ключей |

|

|

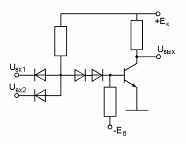

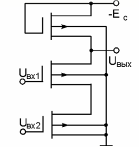

| ДТЛ диодно-транзисторная логика | микросхема на базе биполярных транзисторов, диодов и резисторов. |

|

|

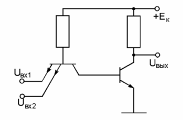

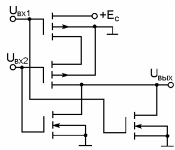

| ТТЛ транзисторно-транзисторная логика | микросхемы сделаны из биполярных транзисторов с многоэмиттерными транзисторами на входе |

|

|

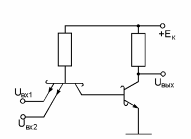

| ТТЛШ транзисторно-транзисторная логика с диодами Шоттки | усовершенствованная ТТЛ, в которой используются биполярные транзисторы с эффектом Шоттки |

|

|

| p-МДПТЛ логика на МДП-транзисторах | логика на МДП-транзисторах |

|

|

| КМДПТЛ комплементарная МОП-логика | каждый логический элемент микросхемы состоит из пары взаимодополняющих (комплементарных) полевых транзисторов (n-МОП и p-МОП) |

|

|

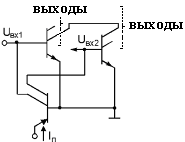

| И2Л интегральная инжекционная логика | микросхемы сделаны на базе биполярных транзисторов |

|

|

| ЭСЛ эмиттерно-связанная логика | на биполярных транзисторах, режим работы которых подобран так, чтобы они не входили в режим насыщения |

|

|

В последнее время все более распространенной и привычной элементной базой для разработчиков цифровых устройств становятся программируемые логические интегральные схемы (ПЛИС). Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле, многие ведущие производители либо начали серийное производство, либо анонсировали ПЛИС с эквивалентной емкостью более 1 миллиона логических вентилей.

Все логические устройства можно разделить на две группы :

1) комбинационные, в которых выходные сигналы в данный момент однозначно определяются входными сигналами. Они используются в информационно-измерительных системах и ЭВМ, в системах автоматического управления, в устройствах промышленной автоматики и т.п. Это шифраторы, дешифраторы, кодопреобразователи, устройства сравнения (компараторы), мультиплексоры, демультиплексоры, сумматоры, арифметико-логические устройства и др.

2) последовательностные, в которых выходные сигналы зависят не только от входных сигналов, но и от предыдущего состояния устройства. Это триггеры, счетчики, регистры, и др.

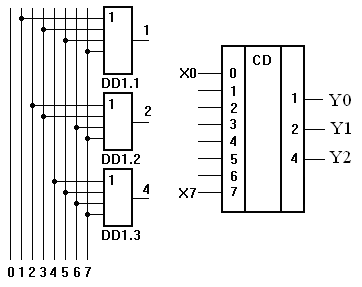

Шифратор

Шифратор (кодер) преобразует сигнал на одном из входов в n-разрядное двоичное число. При появлении сигнала логической единицы на одном из входов на трех выходах шифратора будет присутствовать соответствующее двоичное число. Наибольшее применение находит в устройствах ввода информации.

| Х0 | Х1 | Х2 | Х3 | Х4 | Х5 | Х6 | Х7 | Y2 | Y1 | Y0 | Десятичное число |

Y0 = Х1 V Х3 V Х5 V Х 7

Y1 = Х2 V Х3 V Х6 V Х 7

Y2 = Х4 V Х5 V Х6 V Х 7

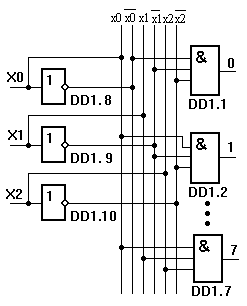

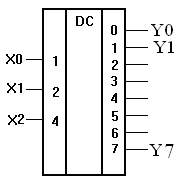

Дешифратор

Дешифратор – это узел, преобразующий код, поступающий на его входы в сигнал только на одном из его выходов. Дешифраторы применяются в устройствах управления, в системах цифровой индикации, и т.д.

| Х2 | Х1 | Х0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| |||

| |||

Триггеры.

Это последовательностные элементы с двумя устойчивыми выходными состояниями (0 или 1), предназначенное для записи и хранения информации. Триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из комбинационных схем. Триггеры входят в состав счетчиков электрических импульсов, регистров, запоминающих устройств.

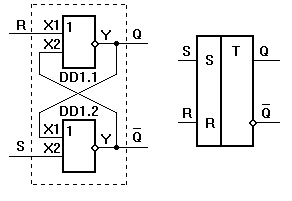

Асинхронный RS-триггер. set - установка и reset - сброс

В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы.

В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами.

Асинхронный RS-триггер с прямыми входами

|

|

|

|

| хранение информации | ||

| запрещенное состояние |

Для триггера с прямыми входами

Q=1 при S=1 и R=0;

Q=0 при S=0 и R=1;

Q равно предыдущему значению Q при S=0 и R=0;

При R=S=1 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера будут одинаковы, а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Такая комбинация является запрещенной и может вывести триггер из строя).

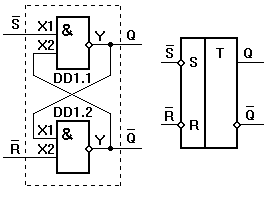

Асинхронный RS-триггер с инверсными входами

|

|

|

|

| запрещенное состояние | ||

| хранение информации |

Для триггера с инверсными входами

Q=1 при S=0 и R=1;

Q=0 при S=1 и R=0;

Q равно предыдущему значению Q при S=1 и R=1;

При R=S=0 состояние триггера будет неопределенным.

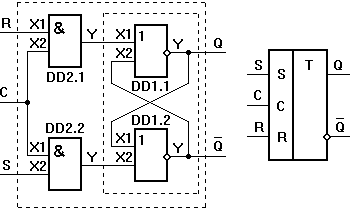

Синхронный RS-триггер.

В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

Синхронный RS-триггер с прямыми входами со статическим управлением.

|

|

|

|

|

| хранение информации | |||

| хранение информации | |||

| хранение информации | |||

| хранение информации | |||

| хранение информации | |||

| запрещенное состояние |

При С=0 на входах R, S асинхронного триггера на элементах DD1.1 и DD1.2 действуют сигналы логического нуля , поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется.

При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами. Статический вход не теряет своего управляющего действия, пока на нем присутствует тактовый (синхро) импульс

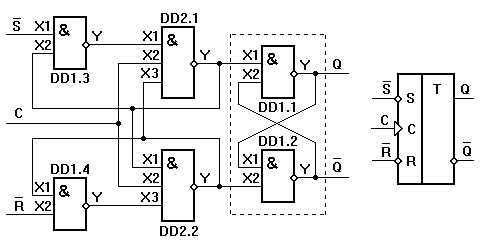

Синхронный RS-триггер с инверсными входами с динамическим управлением.

Динамический синхровход воздействует на состояние выходов триггера в момент своего появления (передним фронтом) или окончания (задним фронтом).

Состояние триггера не меняется при изменении сигналов на входах S и R при С=0 и при С=1 (если триггер уже переключился по фронту синхронизирующего импульса).

Состояние триггера изменится только на фронте синхронизирующего импульса С.