|

|

Назначение и принцип построения четырехразрядных двоичных сумматоров с параллельным переносом

Основной операцией при выполнении арифметических действий в современных цифровых системах является сложение. Поэтому основным блоком операционных устройств обычно является сумматор, который используется также для вычитания, умножения, деления, преобразования чисел в дополнительный код, код «с избытком 3» и в ряде других операций [7, 8, 9].

Суммирование многоразрядных двоичных чисел производится путем их поразрядного сложения с переносом между разрядами. Поэтому основным узлом многоразрядных сумматоров является комбинационный одноразрядный сумматор, который выполняет арифметическое сложение одноразрядных двоичных чисел ai, bi и переноса из соседнего младшего разряда ci, образуя на выходах значение суммы Si и переноса в старший разряд Ci+1.

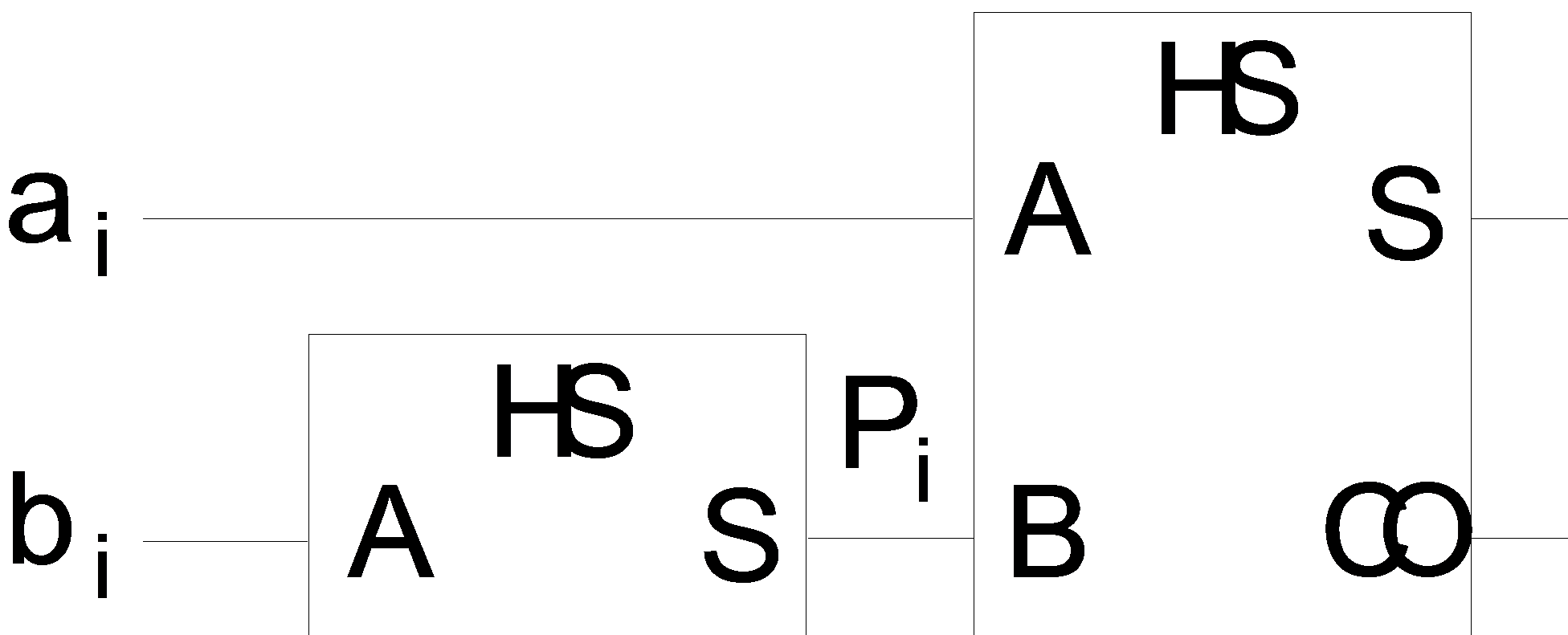

УГО одноразрядного двоичного сумматора представляет собой прямоугольник с аббревиатурой SM (от англ. Summator) во внутреннем поле (рисунок 2.3).

Рисунок 2.3 – Условное графическое обозначение одноразрядного сумматора

В таблице 2.2 приведена таблица истинности одноразрядного сумматора.

Таблица 2.2 – Таблица истинности одноразрядного сумматора

| ai | bi | ci | Si | Ci+1 |

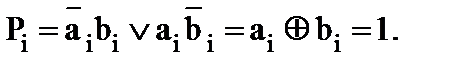

Логические функции для выходов Si и Ci+1 одноразрядного сумматора, записанные в СДНФ по данным таблицы 2.2, после минимизации имеют вид:

(2.1)

(2.1)

(2.2)

(2.2)

Как следует из выражения (2.1), функцию Si удобно реализовать с помощью двух логических элементов «Исключающее ИЛИ», которые часто называют полусумматорами. Функциональная схема одноразрядного сумматора на основе двух полусумматоров показана на рисунке 2.4.

Рисунок 2.4 – Функциональная схема одноразрядного сумматора на основе двух полусумматоров

Для суммирования двух многоразрядных двоичных чисел на каждый разряд необходим один одноразрядный сумматор. Только в младшем разряде можно использовать полусумматор. На рисунке 2.5 приведена функциональная схема четырехразрядного параллельного сумматора с последовательным переносом.

Рисунок 2.5 – Функциональная схема четырехразрядного параллельного сумматора с последовательным переносом

В ее младшем разряде также используется полный одноразрядный сумматор. При этом наличие входа переноса C0 позволяет рассматривать схему как четырехразрядную секцию сумматора с большой разрядностью. Такая секция может быть реализована в виде микросхемы.

Существенным недостатком сумматоров с последовательным переносом является большая задержка (tзд.Cn) выходного переноса сигнала Cn в цепи переноса, связанная с его последовательным прохождением через все одноразрядные сумматоры, каждый из которых имеет задержку переноса tзд. с. В результате tзд.Cn = ntзд.c, а задержка образования n-го разряда суммы

tзд. Sn = tзд S + (n – 1) tзд.C, где tзд.S – задержка суммы одноразрядного сумматора. При числе разрядов n > 4…8 времена tзд.Sn, tзд.Cn оказываются весьма значительными, поэтому для повышения быстродействия в сумматорах обычно применяют ускоренные способы формирования переноса.

Наиболее часто используется одновременное (параллельное) формирование переноса для нескольких разрядов. При этом вводятся вспомогательные функции генерации переноса  и распространения переноса

и распространения переноса  . Тогда выражение (2.2) можно представить в следующем виде:

. Тогда выражение (2.2) можно представить в следующем виде:

(2.3)

(2.3)

Из выражения (2.3) следует, что сигнал переноса на выходе i‑го разряда генерируется самим разрядом (Gi = 1) при ai = bi = 1 независимо от результата переноса из соседнего младшего разряда. Следовательно, можно передавать сигнал переноса для обработки старших разрядов, не дожидаясь окончания формирования переносов из младших разрядов. Однако если только один из сигналов ai, bi равен единице, то перенос в следующий разряд будет иметь место только при наличии переноса из предыдущего разряда (Pi = 1, ci = 1). В этом случае  Именно этот случай будет реализован, если значения функций Gi, Pi снимать с выходов первого полусумматора схемы, показанной на рисунке 2.4.

Именно этот случай будет реализован, если значения функций Gi, Pi снимать с выходов первого полусумматора схемы, показанной на рисунке 2.4.

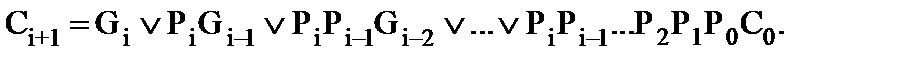

Таким образом, сигналы переноса в каждом разряде формируются одновременно в соответствии с выражением (2.3):

В обобщенном виде получаем:

(2.4)

(2.4)

Для образования переносов C1, C2,…, Ci+1 необходимо предварительно получить функции Pi, Gi для каждого разряда. Как видно из выражения (2.4), сложность функций и, соответственно, схем формирования переноса Ci+1 быстро возрастает при увеличении числа разрядов i. Поэтому данный способ используется при  .

.

Устройство, реализующее функции (2.4), называют схемой ускоренного переноса (СУП). На функциональных схемах его обозначают символом GRP.

Функциональная схема четырехразрядной секции сумматора с ускоренным (параллельным) переносом показана на рисунке 2.6.

Рисунок 2.6 – Функциональная схема четырехразрядной секции сумматора с ускоренным (параллельным) переносом

На рисунке 2.6 изменено условное графическое обозначение одноразрядных сумматоров, так как от них выход переноса Ci+1 не требуется, достаточно одного выхода суммы S. Для реализации ускоренного переноса в одноразрядные сумматоры необходимо ввести дополнительные логические элементы для формирования сигналов Gi, Pi в соответствии с выражением (2.3).