|

|

Последовательностные логические устройства (ПЛУ)

Последовательностные логические устройства (ПЛУ) наряду с комбинационными узлами содержат элементы памяти. Их логическое состояние определяется комбинациями входных переменных как в данный, так и в предыдущие моменты времени.

Триггеры

Простейшими цифровыми устройствами с памятью являются триггеры. Триггеры – электронные устройства, имеющие два устойчивых состояния, способные скачкообразно изменять эти устойчивые состояния под действием входных сигналов и сохранять их в течение заданного времени после окончания действия этих сигналов. Свойство триггеров переходить из одного устойчивого состояния в другое под действием входных сигналов, а также сохранять одно из этих состояний и используется для записи и хранения информации объемом 1 бит.

В зависимости от типа используемых элементов памяти триггеры подразделяются на три класса: статические, динамические и статико-динамические. Рассмотрим работу статических триггеров.

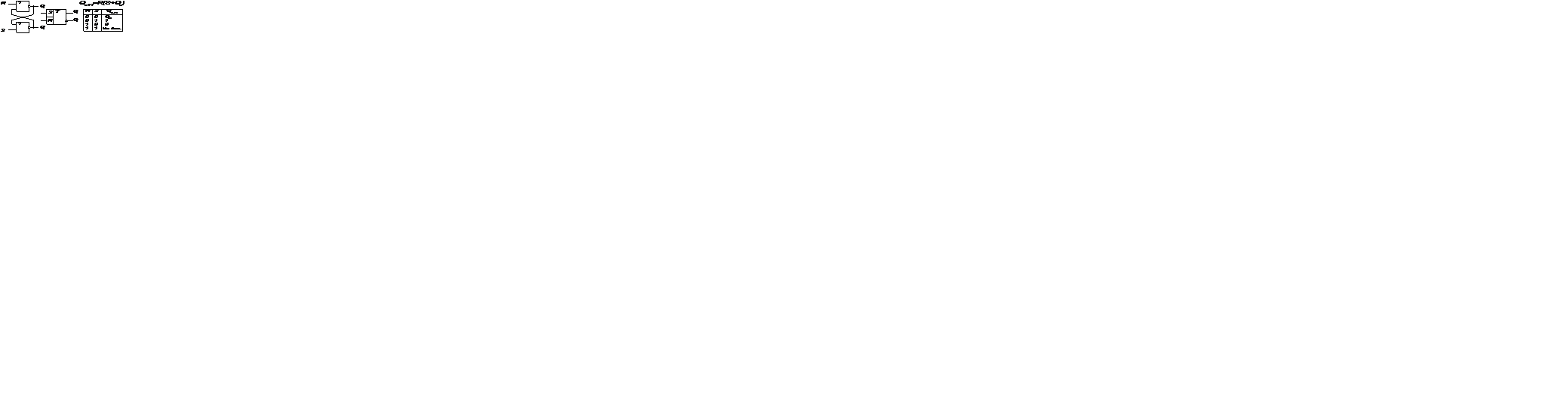

В общем случае статические триггеры (их структура показана на рис. 9.18) содержат схему управления комбинационного типа и элемент памяти – бистабильную ячейку (БЯ), представляющую собой простейший триггер. Состояние триггера определяется значением выходного сигнала  , причем если

, причем если  =1, то

=1, то  =0, а если

=0, а если  =0, то

=0, то  =1. Действие БЯ основано на сильной положительной обратной связи в усилительных цепях с электронными приборами (рис. 9.19).

=1. Действие БЯ основано на сильной положительной обратной связи в усилительных цепях с электронными приборами (рис. 9.19).

| Рис. 9.18. Структурная схема триггера | Рис. 9.19. Бистабильная ячейка на дискретных элементах |

В современной электронике триггеры строятся на основе ЛЭ ИЛИ-НЕ, И-НЕ, передаточные характеристики которых подобны характеристике инвертирующего усилителя. На рис. 9.20 и 9.21 показаны схемы и условные обозначения асинхронных простейших  -триггеров на основе этих ЛЭ. Здесь же представлены характеристические уравнения и таблицы состояний, поясняющие их принцип действия. Они имеют два управляющих (информационных) входа

-триггеров на основе этих ЛЭ. Здесь же представлены характеристические уравнения и таблицы состояний, поясняющие их принцип действия. Они имеют два управляющих (информационных) входа  (set- установка) и

(set- установка) и  (reset- сброс).

(reset- сброс).  -триггер на ЛЭ ИЛИ-НЕ при

-триггер на ЛЭ ИЛИ-НЕ при  = 0, R = 0 сохраняет свое состояние (выполняет функцию хранения информации объемом 1 бит). При

= 0, R = 0 сохраняет свое состояние (выполняет функцию хранения информации объемом 1 бит). При  = 1,

= 1,  = 0 выполняется функция установки (состояние

= 0 выполняется функция установки (состояние  =1), а при

=1), а при  = 0,

= 0,  =1 – функция сброса (состояние

=1 – функция сброса (состояние

= 0). Комбинация входных переменных

= 0). Комбинация входных переменных  =1,

=1,  =1 является запрещенной, так как приводит к логически противоречивому состоянию триггера (

=1 является запрещенной, так как приводит к логически противоречивому состоянию триггера (  =0 и

=0 и  =0) и сама является логически противоречивой (одновременно требуется и установка, и сброс логической единицы на выходе).

=0) и сама является логически противоречивой (одновременно требуется и установка, и сброс логической единицы на выходе).

Рис. 9.20.  - триггер на логических элементах ИЛИ-НЕ

- триггер на логических элементах ИЛИ-НЕ

Если состояние триггера на ЛЭ ИЛИ-НЕ изменяется высоким входным логическим уровнем – 1, то триггер на ЛЭ И-НЕ переключается (инверсным) низким уровнем – 0. В асинхронных триггерах вход синхронизации отсутствует, и переключение триггера происходит одновременно с подачей на управляющие входы соответствующей комбинации управляющих сигналов, что может приводить к ошибкам в работе сложных цифровых систем. Входные сигналы для триггеров могут проходить разный по длине путь, разные стадии обработки, и даже незначительная разница во времени поступления этих сигналов на входы будет порождать кратковременные ошибочные выходные сигналы. Для исправления этого недостатка принято триггеры синхронизировать – разрешать их работу начиная с того момента времени, когда на их входы гарантированно поступят правильные сигналы даже от самых удаленных частей цифровой системы. Далее идет блокировка выходных состояний триггеров на необходимый для данной системы период ожидания, после чего этот цикл снова повторяется.

Рис. 9.21.  - триггер на логических элементах И-НЕ

- триггер на логических элементах И-НЕ

Синхронные триггеры имеют вход синхронизации  (clock) и синхронизируются уровнем или фронтом синхроимпульса. Триггеры, синхронизируемые уровнем, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих управляющих сигналов. В течение паузы между синхроимпульсами состояние триггера остается неизменным. Триггеры, синхронизируемые фронтом, могут изменять свое состояние при поступлении на вход синхронизации соответствующего фронта (положительного или отрицательного) синхроимпульса, т.е. за время действия одного синхроимпульса такой триггер может переключиться только один раз. Триггеры могут быть одноступенчатыми и двухступенчатыми. В одноступенчатых триггерах выходные сигналы изменяются одновременно с изменением входных сигналов. На рис. 9.22 приведены схема

(clock) и синхронизируются уровнем или фронтом синхроимпульса. Триггеры, синхронизируемые уровнем, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих управляющих сигналов. В течение паузы между синхроимпульсами состояние триггера остается неизменным. Триггеры, синхронизируемые фронтом, могут изменять свое состояние при поступлении на вход синхронизации соответствующего фронта (положительного или отрицательного) синхроимпульса, т.е. за время действия одного синхроимпульса такой триггер может переключиться только один раз. Триггеры могут быть одноступенчатыми и двухступенчатыми. В одноступенчатых триггерах выходные сигналы изменяются одновременно с изменением входных сигналов. На рис. 9.22 приведены схема  -триггера, синхронизируемого уровнем на логических элементах И-НЕ, его характеристическое уравнение, условное обозначение и временные диаграммы, объясняющие его работу.

-триггера, синхронизируемого уровнем на логических элементах И-НЕ, его характеристическое уравнение, условное обозначение и временные диаграммы, объясняющие его работу.

Рис. 9.22. Одноступенчатый синхронный  - триггер

- триггер

Двухступенчатые триггеры состоят из двух последовательно соединенных одноступенчатых синхронных триггеров – ведущего и ведомого. На рис. 9.23а,б приведены схема и условное обозначение двухступенчатого  -триггера. Синхронизация работы ведущего и ведомого триггеров осуществляется взаимно инверсными значениями входного синхроимпульса, поэтому они никогда не могут быть включены одновременно, что исключает мгновенную передачу информации со входа на выход. Процесс переключения триггеров поясняют зависимости синхросигналов рис. 9.23в. Передним фронтом входного синхроимпульса (в момент времени

-триггера. Синхронизация работы ведущего и ведомого триггеров осуществляется взаимно инверсными значениями входного синхроимпульса, поэтому они никогда не могут быть включены одновременно, что исключает мгновенную передачу информации со входа на выход. Процесс переключения триггеров поясняют зависимости синхросигналов рис. 9.23в. Передним фронтом входного синхроимпульса (в момент времени  ) сначала отключается ведомый триггер, сохраняя свое состояние, затем (в момент времени

) сначала отключается ведомый триггер, сохраняя свое состояние, затем (в момент времени  ) ведущий триггер переключается в зависимости от комбинации входных информационных сигналов. Задним фронтом синхроимпульса сначала (в момент времени

) ведущий триггер переключается в зависимости от комбинации входных информационных сигналов. Задним фронтом синхроимпульса сначала (в момент времени  ) отключается ведущий триггер от источника информационных сигналов, а затем (в момент времени

) отключается ведущий триггер от источника информационных сигналов, а затем (в момент времени  ) его состояние записывается в ведомый триггер. Выходной сигнал в двухступенчатых триггерах задерживается относительно управляющих сигналов на величину длительности синхроимпульса.

) его состояние записывается в ведомый триггер. Выходной сигнал в двухступенчатых триггерах задерживается относительно управляющих сигналов на величину длительности синхроимпульса.

а) б) в)

Рис. 9.23. Двухступенчатый  - триггер

- триггер

В зависимости от комбинации управляющих сигналов, вызывающих изменение состояния, триггеры подразделяются на функциональные типы. Тип триггера определяется по его характеристическому уравнению или таблице состояний, которые указывают значения выходного сигнала  после переключения триггера (в момент времени

после переключения триггера (в момент времени  ) в зависимости от значений управляющих сигналов и выходного сигнала

) в зависимости от значений управляющих сигналов и выходного сигнала  до переключения триггера (в момент времени

до переключения триггера (в момент времени  ). В цифровых устройствах наиболее часто используются триггеры

). В цифровых устройствах наиболее часто используются триггеры  -,

-,  -,

-,  - и

- и  - типов. Буквами

- типов. Буквами  ,

,  ,

,  ,

,  ,

,  ,

,  и другими принято обозначать управляющие входы триггеров соответствующих типов.

и другими принято обозначать управляющие входы триггеров соответствующих типов.

На рис. 9.24 представлены вариант схемы двухступенчатого  -триггера, синхронизируемого фронтом, его условное обозначение, таблица состояний и его характеристическое уравнение, в котором под сигналом C теперь будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта и значение логической единицы после поступления синхронизирующего сигнала.

-триггера, синхронизируемого фронтом, его условное обозначение, таблица состояний и его характеристическое уравнение, в котором под сигналом C теперь будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта и значение логической единицы после поступления синхронизирующего сигнала.  -триггер также имеет два управляющих входа

-триггер также имеет два управляющих входа  (jump) и

(jump) и  (keep) и отличается от

(keep) и отличается от  -триггера тем, что не имеет запрещенных комбинаций входных сигналов. При поступлении на входы комбинации

-триггера тем, что не имеет запрещенных комбинаций входных сигналов. При поступлении на входы комбинации  =1,

=1,  =1 данный

=1 данный  -триггер под действием заднего фронта синхроимпульса меняет свое состояние на инверсное, т.е.

-триггер под действием заднего фронта синхроимпульса меняет свое состояние на инверсное, т.е.  .

.

Рис. 9.24.  -триггер

-триггер

Варианты одноступенчатого и двухступенчатого  -триггера, условные обозначения, характеристическое уравнение и временные зависимости входных и выходных сигналов двухступенчатого

-триггера, условные обозначения, характеристическое уравнение и временные зависимости входных и выходных сигналов двухступенчатого  -триггера представлены на рис. 9.25.

-триггера представлены на рис. 9.25.

-триггер имеет один управляющий вход

-триггер имеет один управляющий вход  (delay) и выполняет функцию задержки информации, поступающей на вход

(delay) и выполняет функцию задержки информации, поступающей на вход  ,до прихода высокого уровня синхроимпульса для одноступенчатого триггера или ближайшего управляющего фронта синхросигнала в случае двухступенчатого триггера.

,до прихода высокого уровня синхроимпульса для одноступенчатого триггера или ближайшего управляющего фронта синхросигнала в случае двухступенчатого триггера.  -триггер – всегда синхронный. Он может быть построен на основе синхронного

-триггер – всегда синхронный. Он может быть построен на основе синхронного  -триггера или

-триггера или  -триггера исключением комбинаций

-триггера исключением комбинаций  =

=  либо

либо  =

=  . Это достигается, как видно из рис. 9.25, соединением входов

. Это достигается, как видно из рис. 9.25, соединением входов  и

и  либо

либо  и

и  через инвертор.

через инвертор.

Рис. 9.25. Варианты построения  -триггера

-триггера

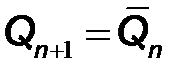

-триггер называется счетным триггером. Он имеет один вход

-триггер называется счетным триггером. Он имеет один вход  . Состояние этого триггера меняется на противоположное (

. Состояние этого триггера меняется на противоположное (  ) при поступлении на вход управляющего фронта сигнала

) при поступлении на вход управляющего фронта сигнала  и сохраняется неизменным до поступления очередного фронта сигнала

и сохраняется неизменным до поступления очередного фронта сигнала  . Поскольку состояние

. Поскольку состояние  -триггера при

-триггера при  =1,

=1,  =1 изменяется на противоположное каждым синхроимпульсом, такой режим его использования соответствует

=1 изменяется на противоположное каждым синхроимпульсом, такой режим его использования соответствует  -триггеру; при этом вход синхронизации

-триггеру; при этом вход синхронизации  является счетным входом.

является счетным входом.  -триггер также выполняет функции

-триггер также выполняет функции  -триггера, если вход

-триггера, если вход  соединяется с инверсным выходом

соединяется с инверсным выходом  . На рис. 9.26 приведены варианты схем

. На рис. 9.26 приведены варианты схем  -триггеров, условные обозначения и характеристическое уравнение, в котором под переменной T также будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта на вход и значение логической единицы после поступления синхронизирующего сигнала.

-триггеров, условные обозначения и характеристическое уравнение, в котором под переменной T также будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта на вход и значение логической единицы после поступления синхронизирующего сигнала.

Рис. 9.26. Счетный  -триггер

-триггер

В синхронных триггерах различных типов часто вводят входы предварительной установки  и сброса

и сброса  . Подачей сигналов на эти входы можно асинхронно изменять состояние выхода

. Подачей сигналов на эти входы можно асинхронно изменять состояние выхода  до прихода синхроимпульсов.

до прихода синхроимпульсов.

На базе триггеров в сочетании с базовыми ЛЭ и КЛУ создаются последовательностные логические устройства, выполняющие ряд важных функций в цифровых устройствах. Наибольшее применение находят ПЛУ типа: счетчики, регистры, генераторы чисел (кодов).

Счетчики.

Счетчики - это последовательностные логические устройства, на выходах которых образуется число, соответствующее количеству поступивших на вход импульсов. Основным параметром счетчика является модуль счета  – максимальное число импульсов, которое может посчитать счетчик, и после поступления которых счетчик возвращается в исходное состояние. Разрядность счетчика равна числу триггеров, используемых в счетчике. Поэтому, счетчик, имеющий m разрядов, имеет 2m устойчивых состояний, а его модуль счета

– максимальное число импульсов, которое может посчитать счетчик, и после поступления которых счетчик возвращается в исходное состояние. Разрядность счетчика равна числу триггеров, используемых в счетчике. Поэтому, счетчик, имеющий m разрядов, имеет 2m устойчивых состояний, а его модуль счета  может быть равным или меньше 2m. Двоичный счетчик имеет модуль счета

может быть равным или меньше 2m. Двоичный счетчик имеет модуль счета

=2m. Когда модуль счета меньше целой степени числа 2 (

=2m. Когда модуль счета меньше целой степени числа 2 (  <2m) счетчик называется двоично-кодированным. Количество поступивших на счетный вход импульсов представляется на выходах счетчика в виде двоичного числа в прямом или обратном коде. Обычно счетчики имеют вспомогательные входы установки

<2m) счетчик называется двоично-кодированным. Количество поступивших на счетный вход импульсов представляется на выходах счетчика в виде двоичного числа в прямом или обратном коде. Обычно счетчики имеют вспомогательные входы установки  , позволяющие предварительно установить на выходах заданное число, и входы сброса

, позволяющие предварительно установить на выходах заданное число, и входы сброса  , подача сигнала на которые переводит счетчик в исходное состояние. Частота импульсов на выходе последнего разряда счетчика в

, подача сигнала на которые переводит счетчик в исходное состояние. Частота импульсов на выходе последнего разряда счетчика в  раз меньше частоты импульсов, поступающих на его вход. Поэтому счетчики широко используются в качестве делителей частоты. По типу функционирования счетчики подразделяются на суммирующие, вычитающие, реверсивные. По организации счета различают последовательные, параллельные, параллельно-последовательные, асинхронные, синхронные счетчики. Основу счетчиков составляют счетные триггеры, которые образуются из

раз меньше частоты импульсов, поступающих на его вход. Поэтому счетчики широко используются в качестве делителей частоты. По типу функционирования счетчики подразделяются на суммирующие, вычитающие, реверсивные. По организации счета различают последовательные, параллельные, параллельно-последовательные, асинхронные, синхронные счетчики. Основу счетчиков составляют счетные триггеры, которые образуются из  - или

- или  -триггеров. Вариант схемы последовательного асинхронного двоичного счетчика с модулем счета

-триггеров. Вариант схемы последовательного асинхронного двоичного счетчика с модулем счета  =16, а также, временные зависимости входного и выходных сигналов, поясняющие его работу, и УГО показаны на рис. 9.27.

=16, а также, временные зависимости входного и выходных сигналов, поясняющие его работу, и УГО показаны на рис. 9.27.

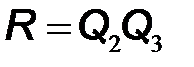

Примером двоично-кодированных счетчиков могут служить счетчики с модулем счета  =10 и 6. При построении счетчиков с произвольным модулем счета получили распространение два метода: метод модификации межразрядных связей и метод управления сбросом. Так, например, двоично-десятичный счетчик с модулем счета

=10 и 6. При построении счетчиков с произвольным модулем счета получили распространение два метода: метод модификации межразрядных связей и метод управления сбросом. Так, например, двоично-десятичный счетчик с модулем счета  =10 можно реализовать на основе шестнадцатеричного счетчика показанного на рис. 9.27, организовав подачу сигнала на вход сброса

=10 можно реализовать на основе шестнадцатеричного счетчика показанного на рис. 9.27, организовав подачу сигнала на вход сброса  .

.

а)

б) в)

Рис. 9.27. Асинхронный двоичный счетчик с модулем счета  =16:

=16:

а) структурная схема;

б) временные диаграммы напряжений синхроимпульсов, поясняющие принцип работы;

в) условное графическое обозначение

Регистры.

Регистрами называются многофункциональные последовательностные устройства, которые выполняют ряд операций над многоразрядными цифровыми кодами: запись, хранение, выдачу информации, сдвиг информации в разрядной сетке вправо или влево, поразрядные логические операции.

Регистры находят широкое применение в различных устройствах цифровой электроники. Например, регистры используются для кратковременного хранения небольшого объема информации. В компьютерах они исполняют роль сверхоперативных запоминающих устройств.

Регистры классифицируют по различным признакам. По способу синхронизации различают однотактные, двухтактные и многотактные регистры. По количеству линий передачи информации различают однофазные и парафазные регистры. Главным признаком классификации регистров является способ приема и выдачи информации. По этому признаку различают параллельные регистры; последовательные (сдвигающие) регистры и параллельно-последовательные регистры.

Параллельный регистр. Пример схемы параллельного регистра, построенного на  -триггерах, показан на рис. 9.28а. В каждый

-триггерах, показан на рис. 9.28а. В каждый  -триггер может быть записана, храниться и считываться информация одного разряда, в нашем случае, четырехразрядного слова. Схемы разрядов не связаны между собой. Для всех триггеров общей является цепь синхронизации. При подаче на вход

-триггер может быть записана, храниться и считываться информация одного разряда, в нашем случае, четырехразрядного слова. Схемы разрядов не связаны между собой. Для всех триггеров общей является цепь синхронизации. При подаче на вход  регистра импульса синхронизации выполняется запись в

регистра импульса синхронизации выполняется запись в  -триггеры информации в виде прямого цифрового кода в параллельной форме. С приходом этого же импульса синхронизации произойдет очистка тех

-триггеры информации в виде прямого цифрового кода в параллельной форме. С приходом этого же импульса синхронизации произойдет очистка тех  -триггеров, в которые будет записываться логические нули, поступившего на вход регистра цифрового кода. Таким образом, рассматриваемый регистр является однотактным параллельным регистром с однофазным входом. В приведенной схеме информация сохраняется до прихода следующего импульса синхронизации на вход

-триггеров, в которые будет записываться логические нули, поступившего на вход регистра цифрового кода. Таким образом, рассматриваемый регистр является однотактным параллельным регистром с однофазным входом. В приведенной схеме информация сохраняется до прихода следующего импульса синхронизации на вход  регистра. На промежутках времени между двумя синхроимпульсами

регистра. На промежутках времени между двумя синхроимпульсами  хранимая информация может считываться с выхода регистра в виде параллельного прямого кода. Цепи управления считыванием информации на рис. 9.28 не показаны. В современной схемотехнике регистры строят преимущественно на двухступенчатых

хранимая информация может считываться с выхода регистра в виде параллельного прямого кода. Цепи управления считыванием информации на рис. 9.28 не показаны. В современной схемотехнике регистры строят преимущественно на двухступенчатых  -триггерах или на

-триггерах или на  -триггерах с динамическим управлением. На рис. 9.28б показано условное графическое обозначение параллельного регистра.

-триггерах с динамическим управлением. На рис. 9.28б показано условное графическое обозначение параллельного регистра.

а) б)

Рис. 9.28. Параллельный регистр:

а) структурная схема;

б) условное графическое обозначение

Сдвигающий регистр. Сдвигающие регистры представляют собою последовательную цепочку разрядных схем. На  -триггерах схема последовательного однотактного регистра со сдвигом вправо показана на рис. 9.29а. Условное графическое обозначение такого регистра представлено на рис. 9.29б. Цепь синхронизации для всех триггеров является общей. Принцип записи четырехразрядного прямого последовательного цифрового кода

-триггерах схема последовательного однотактного регистра со сдвигом вправо показана на рис. 9.29а. Условное графическое обозначение такого регистра представлено на рис. 9.29б. Цепь синхронизации для всех триггеров является общей. Принцип записи четырехразрядного прямого последовательного цифрового кода  в регистр поясняет, приведенная ниже таблица. При поступлении на вход

в регистр поясняет, приведенная ниже таблица. При поступлении на вход  первого синхроимпульса в регистр записывается один младший разряд цифрового кода (слова). С поступлением каждого следующего синхроимпульса производится запись следующего старшего разряда со сдвигом кода вправо в триггеры младших разрядов. Для записи

первого синхроимпульса в регистр записывается один младший разряд цифрового кода (слова). С поступлением каждого следующего синхроимпульса производится запись следующего старшего разряда со сдвигом кода вправо в триггеры младших разрядов. Для записи  - разрядного кода сам регистр должен содержать

- разрядного кода сам регистр должен содержать  триггеров, а на его вход надо подать

триггеров, а на его вход надо подать  синхроимпульсов.

синхроимпульсов.

Рис. 9.29. Сдвигающий регистр

а) структурная схема;

б) условное графическое обозначение

Хранимую в сдвигающем регистре информацию в виде последовательного кода можно считать, подав на вход регистра последовательность из  синхроимпульсов. Как показано на рис. 9.29а, информацию можно также считывать в виде параллельного прямого кода. Используя на выходе сдвигающего регистра схемы управления из КЛУ, хранимую информацию можно считывать в виде последовательного или параллельного, прямого или обратного цифрового кода, т.е. регистр, может выполнять функции преобразователя кодов.

синхроимпульсов. Как показано на рис. 9.29а, информацию можно также считывать в виде параллельного прямого кода. Используя на выходе сдвигающего регистра схемы управления из КЛУ, хранимую информацию можно считывать в виде последовательного или параллельного, прямого или обратного цифрового кода, т.е. регистр, может выполнять функции преобразователя кодов.

Таблица 9.5

Пояснение последовательной записи

цифрового кода в сдвигающий регистр

| № синхро-импульса |

|

|

|

|

| - | - | - | |

|

| - | - | |

|

|

| - | |

|

|

|

|

Сдвигающий регистр задерживает передачу информации на  тактов машинного времени. Это используется в вычислительной технике для согласования процесса обмена информацией между устройствами, работающими в различных масштабах времени (с различным быстродействием).

тактов машинного времени. Это используется в вычислительной технике для согласования процесса обмена информацией между устройствами, работающими в различных масштабах времени (с различным быстродействием).

Разновидностью сдвигающего регистра является реверсивный регистр. В реверсивном регистре для изменения направления сдвига (вправо – влево) организуют межразрядные связи между соседними триггерами с помощью КЛУ. Реверсивные регистры используются в арифметико-логических устройствах для выполнения операций умножения и деления.