|

|

Вычислитель двоичных чисел

В вычислительных устройствах вычитание преобразуется в сложение путем суммирования дополнения вычитаемого Q с уменьшаемым P.

- 5

+ 2

+ 2

Уменьшаемое P

Вычитаемое Q

Результат Σ со знаком «+»

P Q

0 1 1 1

0 1 0 1

Второе дополнение от Q образуется путем инвертирования каждого бита (1-ое дополнение) и его последующего сложения с «1».

1 0 1 0

1 0 1 0

+ 1

1 0 1 1 2-ое дополнение Q

1 0 1 1 2-ое дополнение Q

0 1 1 1 P

+ 1 0 1 1 2-ое дополнение

10 0 1 0

Образующийся при сложении перенос не является результатом вычитания, но может быть использован для определения численных значений. Так как в двоично-кодированных числах положительный знак представлен через «0», то перенос в схеме должен отрицаться.

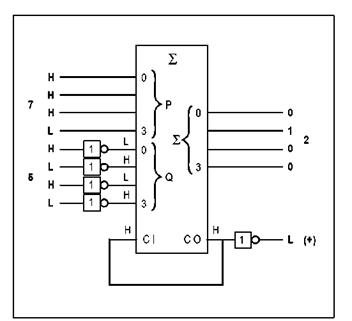

На рисунке 6.1.5.1 представлена схема вычитания, когда уменьшаемое больше вычитаемого.

Рисунок 6.1.5.1 Уменьшаемое > вычитаемое

Путем соединения CI и CO образуется 2-ое дополнение.

Если результат вычитания отрицательный, то на выходе требуется образование второго дополнения:

|

5 Уменьшаемое P

- 7 Вычитаемое Q

-  2 Результат Σ со знаком «-»

2 Результат Σ со знаком «-»

P 0 1 0 1

Q 0 1 1 1

1 0 0 0

1 0 0 0

+ 1

1 0 0 1 2-ое дополнение Q

1 0 0 1 2-ое дополнение Q

0 1 0 1 P

+ 1 0 0 1 2-ое дополнение

01 1 1 0 2-ое дополнение результата Σ

0 0 0 1

0 0 0 1

+ 1

+ 1

0 0 1 0

На рисунке 6.1.5.2 представлена схема вычитания, когда уменьшаемое меньше вычитаемого.

В схеме на рисунке 6.1.5.2 нет сложения «1», так как она должна появиться как на входе, так и на выходе.

Рисунок 6.1.5.2 Уменьшаемое < вычитаемое

Экспериментальная часть

Полусумматор

❒ Эксперимент 1: Полусумматор, состоящий из основных элементов

Ход работы:

· Создайте полусумматор, который состоит только из основных элементов, и дополните схему сложения, представленную на рисунке 6.2.1.1.

· В таблицу 6.2.1.1 занесите выходные величины всех логических элементов для заданных входных величин.

· Проверьте схему и таблицу с помощью Digital Trainingssystem.

| Слагаемые | Выходы логических элементов | Сумма | |||||

| P0 | Q0 | D1 | D2 | D3 | D4 | Σ 0 | C1 |

Таблица 6.2.1.1

Рисунок 6.2.1.1 Схема полусумматора, состоящего из основных элементов

❒ Эксперимент 2: Полусумматор, состоящий только из элементов НЕ-И

|

Ход работы:

· Создайте полусумматор, который состоит только из элементов НЕ-И. Дополните схему сложения, представленную на рисунке 6.2.1.2.

· В таблицу 6.2.1.2 занесите выходные величины всех логических элементов для заданных входных величин.

· Проверьте схему и таблицу с помощью Digital Trainingssystem.

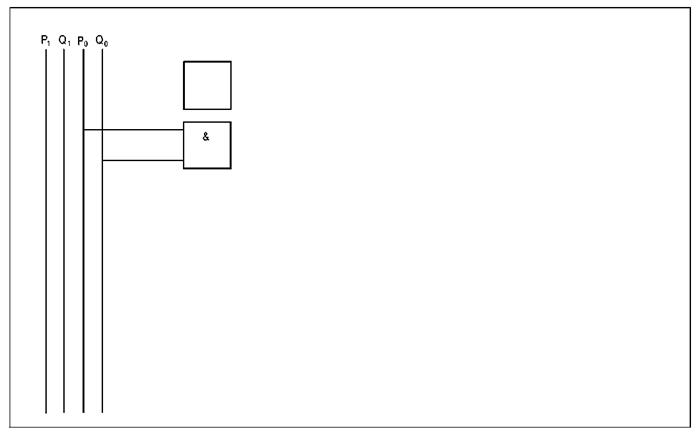

· Полусумматор можно создать также с помощью только двух логических элементов. Дополните схему, представленную на рисунке 6.2.1.3 и проверьте ее с помощью Digital Trainingssystem.

Рисунок 6.2.1.3 Схема

| Слагаемые | Выходы логических элементов | Сумма | ||||||

| P0 | Q0 | D1 | D2 | D3 | D4 | D5 | Σ 0 | C1 |

| Таблица 6.2.1.2 |

| Рисунок 6.2.1.2 Схема полусумматора, состоящего только из элементов НЕ-И |

Полный сумматор

❒ Эксперимент 1: Одноразрядный полный сумматор

Одноразрядный полный сумматор должен быть собран из элементов И, ИЛИ и НЕ.

Ход работы:

· Заполните таблицу 6.2.2.1.

· Составьте с помощью KV-диаграммы (рисунки 6.2.2.1 и 6.2.2.2) минимизированное уравнение для суммы Σ и переноса CO.

· Дополните схему, представленную на рисунке 6.2.2.3 и проверьте ее с помощью Digital Trainingssystem.

| P1 | Q1 | CI | Σ | CO | |

|

|

❒ Эксперимент 2: 2-битный полный сумматор

2-битный полный сумматор должен быть создан из дискретно созданных полусумматоров.

Ход работы:

· Заполните таблицу 6.2.2.2.

· Дополните схему, представленную на рисунке 6.2.2.4.

· Проверьте 2-битный полный сумматор с помощью Digital Trainingssystem.

· Для проверки занесите в схему соединений данные для сложения двоичных чисел P = 01 и Q = 11.

| P1 | Q1 | P0 | Q0 | CO | Σ 1 | Σ 0 | ||||

Таблица 6.2.2.2

Рисунок 6.2.2.4 Схема 2-битного полного сумматора