|

|

Схемы сложения двоично-десятичного кода 8421

|

❒ Эксперимент 1: Сложение двух десятичных чисел

Следует создать схемы, которые позволяют складывать десятичные числа. На рисунке 6.2.3.1 на примере сложения элементов 9 + 9 показана проблема, которая может при этом возникнуть.

Ход работы:

· Соберите корректирующую схему по принципу кодового преобразователя. Имеющийся в таблице 6.2.3.1 алгоритм поможет Вам в этом.

· Заполните таблицу 6.2.3.1 и составьте уравнения функции для Σ0’, Σ1’, Σ2’, Σ3’ и CO’.

· Проверьте с помощью KV-диаграммы, можно ли на рисунках 6.2.3.2 … 6.2.3.5, провести минимизацию. Используйте поля непроизвольного состояния.

· Дополните схему, представленную на рисунке 6.2.3.6 (страница 74) и проверьте ее с помощью Digital Trainingssystem.

Рисунок 6.2.3.1

| Десятичное число | Выходы сумматора («чисто» двоичные) | Исправленный результат (двоично-десятичные коды) | ||||||||

| CO | Σ3 | Σ 2 | Σ 1 | Σ 0 | CO’ | Σ 3’ | Σ 2’ | Σ 1’ | Σ 0’ | |

Уравнения функции из таблицы 6.2.3.1:

Σ0 ’ = .................................................................

Σ1’ = .................................................................

= ................................................................

Σ2’ = .................................................................

= ................................................................

| Σ3’ |

= ................................................................

CO’ = ................................................................

= ................................................................

|

|

Минимизированные уравнения из KV-диаграмм:

Σ0’ = .................................................................

Σ1’ = .................................................................

Σ2’ = .................................................................

Σ3’ = .................................................................

CO’ = ................................................................

|

|

’

’

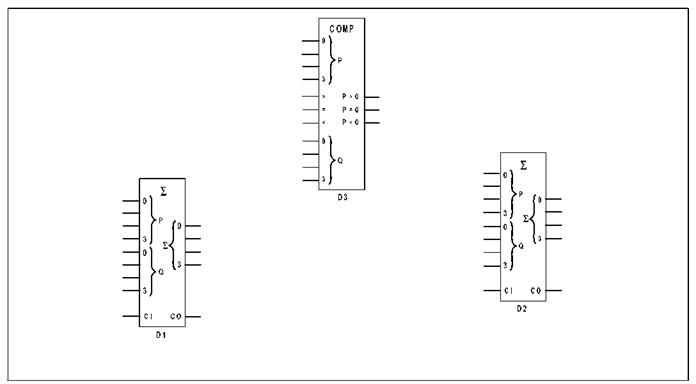

Рисунок 6.2.3.6 Схема

Примечания:

❒ Эксперимент 2: Упрощенная корректирующая схема

С помощью 4-битного полного сумматора можно намного проще выполнить необходимую корректировку эксперимента 1.

Ход работы:

· Дополните схему, представленную на рисунке 6.2.3.7.

· В соответствии с каждой переключательной схемой обозначьте на схеме логические величины.

Рисунок 6.2.3.7 Упрощенная корректирующая схема

Вопрос 1: Обоснуйте логические величины на выходе CO второго 4-битного полного сумматора.

Вопрос 1: Обоснуйте логические величины на выходе CO второго 4-битного полного сумматора.

Ответ: .................................................................

Ответ: .................................................................

...............................................................

...............................................................

...............................................................

...............................................................

❒ Эксперимент 3: Сложение с помощью 4-битного компаратора чисел

Для сложения двух одноразрядных двоичных чисел должна быть собрана схема сложения с использованием 4-битного числового компаратора. Промежуточный итог первого сложения D1 сравнивается компаратором со смежным числом «9». При P < Q (где Q является псевдотетрадой) или при переносе на D1 должно быть исправление с помощью второго сложения D2.

Ход работы:

· Дополните схему, представленную на рисунке 6.2.3.8, и заполните таблицу 6.2.3.2.

· Проверьте схему с помощью Digital Trainingssystem.

Вопрос 1: При проверке схемы установите, что результат оказывается высоким на «1» или «2». О чем следует сразу же подумать?.

Ответ: .................................................................

.............................................................................

.............................................................................

.............................................................................

.............................................................................

.............................................................................

| Пример сложения | Полный сумматор D1 | Компаратор D3 | Полный сумматор D2 | ||||||||||||||||||||

| P3 | P2 | P1 | P0 | Q3 | Q2 | Q1 | Q0 | CO | Σ 3 | Σ 2 | Σ 1 | Σ 0 | P3 | P2 | P1 | P0 | CO | Σ 3 | Σ 2 | Σ 1 | Σ 0 | ||

| 4 + 3 | |||||||||||||||||||||||

| 8 + 4 | |||||||||||||||||||||||

| 8 + 8 | |||||||||||||||||||||||

| 9 + 9 |

Таблица 6.2.3.2

Рисунок 6.2.3.8 Схема

Полувычитатель

❒ Эксперимент 1: Вычитание двух одноразрядных двоичных чисел

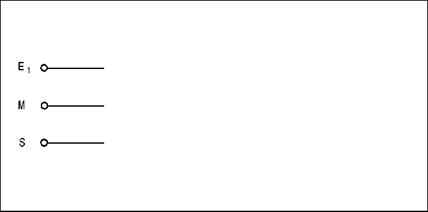

Самой простой схемой вычитания является полувычитатель. Он может вычитать двоичное число (вычитаемое S) из другого двоичного числа (уменьшаемое M).

Ход работы:

· Заполните таблицу 6.2.4.1, учитывая правила вычитания. СокращенияDи E стоят для разности или временных выходов.

· Укажите необходимые для схемы уравнения функции.

· С помощью Digital Trainingssystem могут быть составлены два различных полувычитателя. Дополните схемы, представленные на рисунках 6.2.4.1 и 6.2.4.2.

D = .....................................................................

E = ...................................................................

| M | S | D | E | |

Таблица 6.2.4.1

Рисунок 6.2.4.1 Схема 1

|

Вопрос 1:Полувычитатели можно использовать только с определенными ограничениями. Обоснуйте это.

Вопрос 1:Полувычитатели можно использовать только с определенными ограничениями. Обоснуйте это.

Ответ: ...............................................................

Ответ: ...............................................................

.............................................................

.............................................................

.............................................................

.............................................................

.............................................................

.............................................................

.............................................................

Рисунок 6.2.4.2 Схема 2

|

Полный вычитатель

❒Эксперимент 1: 1-битный полный вычитатель

Полный вычитатель используют для многоколонного вычитания.

· Указание:При вычитании к значению вычитаемого числа (вычитаемое) прибавляется возможное заимствование (сигнал 1) и из уменьшаемого вычитается увеличенное таким образом вычитаемое.

Ход работы:

· 1-битный полный вычитатель можно без труда составить по тому же алгоритму, что и 1-битный полный сумматор. Дополните таблицу 6.2.5.1.

· Указание:E1 = заимствование из предшествующего разряда вычитания, E2 = заимствование для следующего разряда.

· С помощью KV-диаграммы (рисунок 6.2.5.1) составьте минимизированное уравнение.

· Дополните схему, представленную на рисунке 6.2.5.3 и проверьте ее с помощью Digital Trainingssystem.

Вопрос 1:Сравните дедукцию схемы, представленной на рисунке 6.2.5.3, со схемой 1- битного полного сумматора.

Вопрос 1:Сравните дедукцию схемы, представленной на рисунке 6.2.5.3, со схемой 1- битного полного сумматора.

Ответ: ...............................................................

Ответ: ...............................................................

.............................................................

.............................................................

.............................................................

.............................................................

| M | S | E1 | D | E2 |

Таблица 6.2.5.1

Рисунок 6.2.5.3 Схема 1-битного полного вычитателя

❒ Эксперимент 2: Варианты схем 1-битного полного вычитателя

Если рассматривать образование разности с математической точки зрения, то существует еще два варианта схем с Digital Trainingssystem.

Запомни:

Сумма S + E1 образуется с помощью полусумматора,а получившийся промежуточный итог позволяет получить разность с помощью полувычитателя.

Разность = Уменьшаемое – (вычитаемое + заимствование)

D = M - (S + E1)

|

Ход работы:

· Из математических уравнений создайте первый вариант схемы и дополните рисунок 6.2.5.4.

· Из вышеупомянутого уравнения можно создать еще к вариант 1-битного полного вычитателя. Дополните рисунок 6.2.5.5 и обоснуйте ваше мнение.

Рисунок 6.2.5.41-ый вариант схемы

|

Обоснование:

.......................................................

.......................................................

.......................................................

.......................................................

.......................................................

.......................................................

.......................................................

.......................................................

Рисунок 6.2.5.5 2-ой вариант схемы

|